IBM全球首发2nm制程芯片

2021-05-07 09:58:00

2021-05-07 09:58:00IBM全球首发2nm!3.33亿晶体管/mm²,性能比7nm芯片高45%

5月7日报道,昨日,美国科技企业IBM发布全球首个2nm制程芯片制造技术。

目前该技术仍在概念验证阶段,可能还需几年才能投入市场。路透社报道称,IBM已与三星、英特尔签署了联合开发协议。

▲IBM 2nm制程芯片展示(图源:IBM)

从理论上来说,2nm制程芯片相比现有可量产的7nm、5nm制程芯片,在晶体管密度、性能、功耗等方面能实现大幅提升。

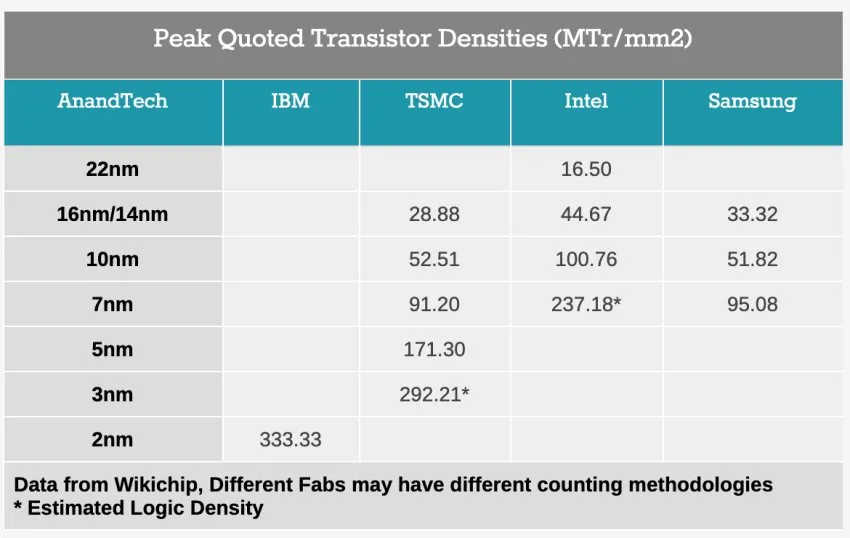

IBM预计,2nm制程技术或能实现在“指甲盖”大小的芯片上集成约500亿晶体管;据国外科技媒体AnandTech报道,IBM 2nm制程或能在每平方毫米芯片上集成3.33亿个晶体管。相比之下,台积电5nm制程每平方毫米约有1.71亿个晶体管,三星5nm制程每平方毫米约有1.27亿个晶体管。

性能和功耗方面,相比7nm芯片,2nm芯片的性能可提升45%、功耗有望降低75%。IBM并未说明对比的7nm芯片是由台积电还是三星生产。

▲IBM、台积电、英特尔、三星各制程节点晶体管密度对比(图源:AnandTech)

01.用纳米级绝缘材料防“漏电”,采用GAA工艺

构成芯片的基本单元晶体管,可被视作是控制电流的开关。随着芯片制造制程渐趋先进,单个晶体管开关的“尺寸”越来越小,其对电流的控制能力受到影响,即使在关闭状态下也可能发生“漏电”。这也是实现先进制程的一大难题。

IBM高级副总裁兼IBM研究院(IBM Research)主管Darío Gil在接受路透社采访时称,IBM科学家通过使用几纳米厚的绝缘材料来阻止电流泄露,以解决上述问题。

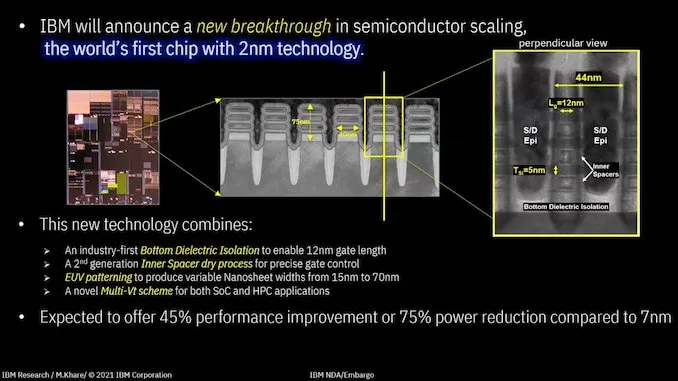

据国外科技媒体AnandTech报道,IBM并未说明其2nm芯片采用的具体工艺,但根据图片推测应为三栈全栅极工艺(three-stack GAA)。目前,台积电和三星在5nm和3nm节点均采用鳍式场效应晶体管(FinFET)结构,在3nm制程之后或将转向GAA工艺。IBM的三栈GAA工艺使用75nm的单元高度,40nm的单元宽度,单个纳米片(nanosheet)的高度为5nm,纳米片间距为5nm,栅间距(CPP)为44nm,栅极长度(gate length)是12nm。据IBM方面分享,2nm制程芯片首次采用了底部电阻隔离通道技术(bottom dieletric isolation channel),使12纳米的栅极长度成为可能;其内部隔离器则采用第二代干法工艺设计,有助于纳米片的开发。此外,2nm制程芯片的基板工序(FEOL)采用了极紫外线光刻(EUV)技术进行加工。

根据IBM发布的新闻稿,2nm制程芯片制造技术,能够助力手机、数据中心、PC、自动驾驶等领域应用实现性能飞跃。

具体来说,在手机领域,2nm制程芯片或能使手机电池续航时间“翻两番”,即用户每4天为手机充电一次。

数据中心目前占据了全球1%的能源消耗,通过将处理器替换为2nm制程产品可大大降低这一数字。

对于PC产品来说,2nm制程芯片有助于加快应用程序处理速度、更容易地翻译语言、更快速地接入互联网。

在自动驾驶领域,2nm芯片能够助力目标检测算法更快运行,进而帮助提升自动驾驶汽车的反应时间。

02.已与三星英特尔签约,采取合作研发模式

在IBM全球首发2nm芯片制造技术背后,该公司在半导体领域已有几十年的研发历史,此前还曾全球首发7nm、5nm芯片制造技术。

Darío Gil称:“这(发布全球首个2nm芯片制造技术)是一个示范,表明了持续投资和合作研发的生态系统能够带来突破性的进展。”

IBM研究院旗下共有12个实验室,分布在美国纽约、加州、德州等多个地区。

据悉,IBM的半导体研发工作主要由位于纽约州首府奥尔巴尼的实验室承担。在该实验室中,IBM科学家与公共或私营部门的合作伙伴共同进行技术攻关。本次发布的2nm芯片制造技术的研发工作也由这个实验室承担。

2014年,IBM将芯片制造业务出售给了美国芯片制造商格罗方德,目前不具备芯片规模量产能力。据路透社报道,IBM已与芯片制造商三星和英特尔签署了使用IBM芯片制造技术的联合开发协议。

▲IBM位于纽约州首府奥尔巴尼的的研发中心(图源:IBM)

03.尚处于概念验证阶段,商用价值仍待挖掘

从理论上来说,IBM发布的2nm芯片制造技术能够较5nm技术实现大幅性能提升。但是,该2nm芯片制造技术还处于概念验证阶段,离具备商用价值任重道远。

目前,全球突破10nm及以下先进制程生产工艺的玩家仅有台积电和三星。两家公司的10nm、7nm、5nm制程均已实现商用,目前正进行3nm攻关。

根据此前台积电公布相关信息,相比5nm制程,3nm相同功耗下性能可提升10~15%,预计能在2021年第四季度实现量产。

|

全球先進制程技術密度對比 |

|||||||||

|

|

臺積電 3nm |

英特爾7nm |

臺積電 5nm |

三星 |

三星 |

英特爾 10nm |

臺積電 7nm |

臺積電 10nm |

三星 10nm |

|

鰭片間距(nm) |

\ |

\ |

25-26 |

\ |

27 |

34 |

40 |

36 |

42 |

|

極間距(nm) |

\ |

\ |

48 |

\ |

54 |

54 |

57 |

66 |

68 |

|

最小金屬間距(nm) |

\ |

\ |

40 |

\ |

\ |

36 |

\ |

42 |

48 |

|

邏輯單元高度(nm) |

\ |

\ |

180 |

\ |

\ |

272 |

\ |

360 |

420 |

|

邏輯電晶體密度(個/mm2) |

2.5億 |

2~2.4億 |

1.713億 |

約1.3億 |

1.0123億 |

1.008億 |

9120萬 |

4810萬 |

5160萬 |

|

邏輯電晶體密度 (相較上一代提升) |

46% |

1倍 |

88% |

28% |

96% |

1倍 |

90% |

48% |

51% |

|

性能(相較上一代提升) |

10-15% |

20% |

15% |

10% |

20% |

25% |

20% |

20% |

27% |

|

功耗(相較上一代降低) |

25-30% |

\ |

30% |

20% |

50% |

45% |

40% |

40% |

40% |

|

|

|||||||||

▲全球先进制程技术密度对比

04.结语:绝缘材料来“救场”,摩尔定律仍有希望

随着芯片制程逼近物理极限,有关“摩尔定律将死”的预言时不时就会出现。但是,每当人类科学站在下一代制程节点“面前”,总有新的技术涌现出来,维持着摩尔定律继续向前发展。目前,IBM全球首发的2nm芯片制造技术距离商用量产还需要更多时间与技术累积。尽管如此,这亦说明了或许这场人类对先进芯片制程的追逐战,远未到达终局。